Как найти SPI-Flash среди прочего/системного железа, и отыскав, ..что можно с ней сделать?

Рассмотрим методы поиска и программирования м/схем BIOS. Кроликом послужит моя плата ASRock 945GCM-S (ICH7, flash MXIC-25L4005, 512Kb, AMI). Для начала, небольшой обзор шины PCI Express..

-------------------------------------

PCI-E против Legacy-PCI

Традиционно, в архитектуре компьютера главной системной артерией была параллельная шина PCI. К ней, через мосты подключались уже вторичные шины. Такой подход снижал производительность, т.к. шина была общей и всем устройствам приходилось по-братски делить её пропускную способность.

Но с тех-пор утекло уже много воды и на смену параллельной PCI, пришла последовательная PCI-Express (PCI-E, PCIe кому-как нравится) изменив архитектуру системы до неузнаваемости. Вспомним, какие вообще версии PCI-шины существовали и в каком направлении развивался их прогресс:

Код:

Стандарт | Частота | Ширина | Скорость | Тип | ConfigSpace

-------------|----------|---------|-----------|-----------|------------

PCI (v1) 33 MHz 32-бит 133 Мб/с Parallel 256-байт

PCI (v2) 66 MHz 32-бит 266 Мб/с Parallel 256-байт

PCI64 (v2.2) 33 MHz 64-бит 266 Мб/с Parallel 256-байт

PCI64 (v2.3) 66 MHz 64-бит 533 Мб/с Parallel 256-байт

PCI-X (v1) 133 MHz 64-бит 1033 Мб/с Parallel 4096-байт

PCI-X (v2) 266-533 64-бит 4096 Мб/с Parallel 4096-байт

PCI-Express 2.5-GHz 01..32 15872 Мб/с Serial 4096-байт

До явления PCIe народу, ставки делались на частоту и ширину-шины, это давало ожидаемый прирост пропускной способности. Нужно сказать, что 4 Гбайт/с это не плохой результат - отдадим должное разработчикам.. Потом пришла PCI-Express и одним махом отправила все труды на смарку. Шина стала последовательной, и сразу дала прирост х4 - 15 Гигов/сек. Причём она стала параллельно-последовательной, с возможностью масштабирования её ширины в диапазоне 1-32 бит (например PCIE x1/4/16), и это сразу в обоих направлениях. По сути это интеловский клон шины HyperTransport от AMD (всю жизнь вороют друг-у-дружки).

Но вернёмся к топологии материнских плат на основе PCI-Express..

Главным её новшеством является соединение устройств по принципу Point-to-Point (точка-точка). Эта схема предоставляет отдельный канал для передачи данных, каждому из устройств на шине. Делается это посредством коммутатора Switch. Каждое устройство является конечной точкой, а свитч используют для перенаправления данных от устройства к устройству, минуя мост. К рут-комплексу может подключаться несколько свитчей, каждый из которых может иметь свой мост вторичных шин Bridge.

На рисунке ниже - схема PCI-Express, представляющая собой Root-Complex и Switch. К свитчу присоединяются уже сами устройства. Напомню, что каждое из них представляет собой конечную точку "Endpoint". Устройства PCIе можно подключать непосредственно к Root-комплексу - это могут быть всевозможные мосты типа PCIE-to-PCI Bridge, или-же точка в виде графической карты PCI-Express.

Организацию вашей PCIE-системы может показать софт для сбора инфы о машине:

Отчёт PC-Wizard моей системы (i945G chipset)

Код:

> Bus PCI-Express : Да (max. x16)

Number of PEG : 2

>> Bus PCI-Express

Устройство : 82945G/PL PCIe Root Port

Link Width : x16

Link Speed : 2.5 Гб/s

Port : 2

>> Bus PCI-Express

Устройство : Nvidia Corp

Link Width : x16

Link Speed : 2.5 Гб/s

Port : 0

>> Bus PCI-Express

Устройство : 82801G (ICH7 Family) PCIe Root Port

Link Width : x1

Link Speed : 2.5 Гб/s

Port : 1

>> Bus PCI-Express

Устройство : 82801G (ICH7 Family) PCIe Root Port

Link Width : x1

Link Speed : 2.5 Гб/s

Port : 2

Таким образом, в современной архитектуре корневой Root-Complex является чуть-ли не центром вселенной. Он встроен в север и имеет свой блок регистров RCRB. Доступ к этим регистрам открывает его базовый адрес в памяти RCBA - Root Complex Base Address. Буквально все устройства чипсета адресуются через RCBA используя его в качестве базы.

Путешествие к центру вселенной

Инструменты:- Даташит на ICH чипсета (для новых PCH);

- Крутая утилита для просмотра/редактирования памяти "Read & Write Utility";

- Компилятор ассемблера "fasm" (или любой, с окончанием на *asm);

- Виндовый НЕХ-калькулятор.

Как найти RCBA программным способом? Да очень просто! Достаточно скачать даташит на свой чипсет (у меня ICH7) и запустить в нём поиск с ключевым словом "Root Complex Base Address" - упс...

Всякое устройство на PCI-шине имеет в системной памяти своё конфигурационное пространство - ConfigSpace. Стандартный размер этого пространства 256-байт (FFh). Содержимое первых 64-байт (40h) одинаково для всех устройств, а остальные 192-байта специфичны. Каждый байт называют регистром отображённого на память устройства - итого 256-регистров, хотя некоторые из них собираются в слова и двойные слова.

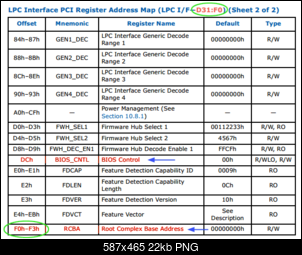

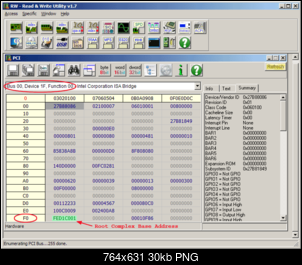

На рисунке выше - скрин старшей части регистров моста PCI-to-LPC. Как оказалось, начиная с ICH7 до PCH, координаты этого моста в системе у всех одинаковы - Bus(0):Dev(1Fh):Func(0). Из даташита видно, что 32-битный RCBA хранится в регистре F0h LPC-моста. Запустим утилиту RW и посмотрим, что находится в этом регистре:

Прокрутив страницу даташита дальше, можно обнаружить описание этого регистра F0h (см.рис.ниже). Там сказано, что младший бит(0) не относится непосредственно к адресу, и логически должен быть сброшен в нуль. Это "бит достоверности адреса", т.е. если он сброшен, то адрес считается недействительным (у меня с ним всё в порядке). Хотя биты(13:1) и указаны как резерв, они обнуляются на аппаратном уровне, в результате чего адрес выравнивается на 14-битную (16-Кбайтную) границу. Отмечу, что Intel указывает координаты Bus:Device:Function в 10-тичном виде 31 - в хексах это будет 1Fh:

Одним словом, свой Root-Complex я могу найти в памяти по адресу 0xFED1C000, и это уже вери-гуд (у вас он может отличаться). В даташите, почти все устройства адресуются через RCBA используя его в качестве базы. Это необходимо учитывать при программировании чипсета. Накатать код мы всегда успеем, но сначала нужно освоить теорию - не зря говорят: -"Не берись за штурвал, не выучив мануал!"

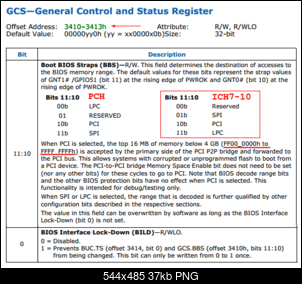

Продолжая поиски котА в дремучем лесу железяк нужно определить, на какой конкретно шине повесился чип SPI-Flash. Знает это один из приоритетных регистров чипсета GCS - 32-битный регистр по смещению 0x3410 от RCBA. В его битах закодировано много-чего, но нас интересует только Flash - остальное в топку:

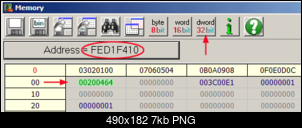

Угу.. выходит чтобы найти GCS, мне нужно к RCBA прибавить 0x3410, считать этот регистр и проверить его биты(11:10). У меня ICH7.., и если они имеют значение(01), то бивис обслуживается интерфейсом SPI. На скрине ниже, значение этого/32-битного регистра в памяти:

Код:

RCBA >> GCS

0xFED1C000 + 0x3410 = 0xFED1F410

----------

0x200464 = 10.0000.0000.0100.0110.0100

++-----------> биты(11:10) = 01 = SPI-Flash

Ладно.. убедился я, что являюсь счастливым обладателем SPI-Flash. Теперь мне нужно найти адрес SPI-контроллёра в памяти, чтобы через него взаимодействовать с чипом ROM-BIOS напрямую. Судя по-всему, инженеры Intel сильно не заморачиваются - его базовый порт они назвали коротко_и_ясно - SPIBAR. Как и большинство девайсов, он имеет своё смещение относительно базы рута RCBA - это offset 0x3020. Здесь упоминается термин RCRB - Root Complex Registers Block, который является синонимом RCBA:

Вот они - регистры контроллёра SPI-Flash. Непосредственная запись и чтение в эти регистры приводят к физическим операциям с чипом BIOS, их активно юзают все программы-прошивальщики. Особое внимание нужно уделить на выделенные зелёным регистр-статуса, и OpСode-Menu. Рассмотрим их подробней..

В регистре статуса, особняком стоит старший бит(15), который можно сравнить со-сторожевым питбулем на входе. Остальные биты определяют характер шинных циклов, кэшировать их или нет, завершилась-ли транзакация удачно, и прочее. Вот перевод на русиш 15-го бита, остальные можете посмотреть у себя в даташите:

Код:

SPI Status Register (SPIBAR + 00h)

----------------------------------

бит 15: - Защита данных SPI - R/W/LO.

0 = Нет защиты - потенциальная опасность!

1 = Конфигурации SPI в смещениях 50h..6Fh изменению не подлежит.

Взведённый бит может быть очищен только аппаратным сбросом Reset.

Тут сказано, что если взвести этот бит-защиты 1-раз, то сбросить его уже не получится - он будет аппаратно удерживаться на протяжении всего сеанса, вплоть до перезагрузки. Поэтому инженерам пришлось здесь сесть на шпагат - или под честное/слово юзера оставить периметр открытым, или-же сделать невозможным процесс настроек SPI-контроллёра. Видимо на всеобщем голосовании был принят первый вариант, т.к. буквально на всех исследуемых мною машинах, этот бит сброшен и защита отключена.

Следующий регистр [OpCode Menu: SPIBAR + 58h] заслуживает ещё большего внимания..

Алгоритм работы со SPI-контроллёром - нестандартный. Коды команд передаются м/схеме ROM не напрямую, а косвенно - через блок регистров "OpCode-Menu". Каждый байт этого/8-байтного регистра содержит один из восьми кодов-операции для м/схемы ROM (она имеет свои регистры). Это могут быть команды: чтения вендора/статуса, запись, стирание, etc.. Платформа не знает, с каким чипом ей предстоит иметь дело, поэтому этот блок-регистров (основываясь на данных текущего чипа ROM) заполняет BIOS при старте платформы:

Код:

SPIBAR = 0xFED1F020 (RCBA + 0x3020)

-----------------------------------

Status = 0004h

OpMenu = 02,03,D8,05,9F,01,06,00 (8-байт)

Интерфейс SPI поддерживает не только 1-байтные, а двух -и даже трёх-байтные команды. В этом случае они записываются в регистр префикса. Например по-умолчанию, запись во-флэш отключена его битом WriteDisable, поэтому перед операцией записи нужно сначала разрешить.., а уже потом производить саму запись. Для этого предназначен префиксный регистр(54h) PrefixOpcode, в котором уже лежит код 04h = WriteDisable (см.скрин выше) - он на старте, и засылается следом за операцией записи во-флэш. В результате получаем снятие защиты только когда это действительно нужно - при записи.

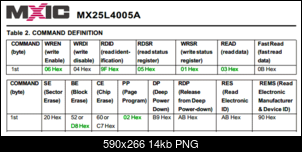

Ниже - скрин опкодов из доки моего чипа MX-25L4005A.

Активные его коды я выделил зелёным - биос прописал их уже в регистр "OpCode-Menu" контроллёра:

Для передачи команды в чип, программа должна передать контроллёру не сам код, а номер байта в 8-байтном блоке OpCode-Menu содержащего код этой команды. Для выбора достаточно 3-х бит. Поскольку расположение кодов в ячейках может быть произвольным и зависит от настроения BIOS, программа должна просканировать весь/8-байтный регистр и найти в нём номер ячейки, в которой хранится код требуемой команды (например 9Fh для ReadID).

Затем, полученный 3-битный номер ячейки отправляется в регистр SPI-Control, где используется как битовое поле Cycle-Opcode-Pointer при формировании 32-битного кода операции для контроллёра SPI. Кроме COP, код-операции содержит инфу о кол-ве передаваемых байт, частоте синхронизации и т.п. Перед началом транзакации на шине SPI, необходимо записать адрес в одноимённый регистр SPI-Address. Затем, циклически опрашивая статус, определяем момент завершения транзакции. Только после этого можно считать данные из регистра SPI-Data(0-7) и считать операцию чтения/записи успешной.

Послесловие..

Признаюсь, что разговарить на эту тему можно бесконечно, ведь это только мизерная часть всего мануала. В нём запросто можно утонуть, если задумаешь охватить всё и сразу. Одних страниц в даташите на чипсет более 800-штук, и в каждой описывается как-минимум по 32 разнообразных бита. При детальном рассмотрении всех регистров можно выловить в системе столько багов, что ни в сказке-сказать, ни пером-описать, ..а только грубым матом - вроде система внушает доверия, а вроде и нет.

На повестке дня - непосредственное программирования чипов BIOS (хотя за сроки не ручаюсь). Использовать буду ассемблер FASM, реальный/нереальный/защищённые моды, регистры чипсета и всё/такое низкоуровневое.

Продолжение следует... |